Un chip di prova con le stesse caratteristiche del prodotto finito mostra la capacità di PowerVia di fornire oltre il 90% di utilizzo delle celle, di superare i colli di bottiglia nelle interconnessioni e di offrire vantaggi competitivi al mercato, inclusi i clienti delle fonderie

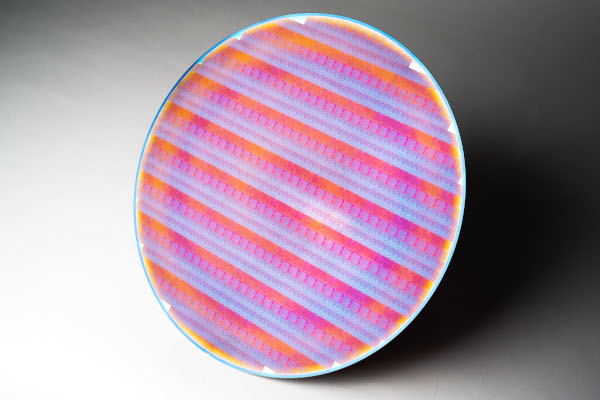

La notizia: Intel è la prima azienda del settore a implementare l’alimentazione dalla parte posteriore di un chip di prova con le stesse caratteristiche del prodotto finito, ottenendo un livello di prestazioni tale da proiettare il mondo verso una nuova era dell’informatica. PowerVia, che sarà inserito sul nodo di processo Intel 20A nella prima metà del 2024, è una soluzione leader nell’alimentazione dalla parte posteriore. Risolve il crescente problema dei colli di bottiglia all’interconnessione dell’area scaling spostando il percorso dell’alimentazione alla parte posteriore del wafer.

PowerVia è un’importante pietra miliare nella nostra ambiziosa strategia ‘cinque nodi in quattro anni’ e nel nostro percorso per ottenere mille miliardi di transistor (one trillion) in un pacchetto nel 2030. Utilizzando un nodo di processo sperimentale e un successivo chip di prova, siamo riusciti a eliminare i rischi connessi all’alimentazione dalla parte posteriore per i nostri nodi di processo, assicurando che Intel sia in vantaggio di un nodo rispetto alla concorrenza nel portare questa tecnologia sul mercato. – Ben Sell, Intel Vice President of Technology Development

Come funziona: Intel ha disaccoppiato lo sviluppo di PowerVia da quello dei transistor per assicurare che fosse pronto per l’implementazione su silicio basata sui nodi di processo Intel 20A e Intel 18A. PowerVia è stato collaudato sul suo stesso nodo di test interno per eseguire il debug e garantire una buona funzionalità della tecnologia prima della sua integrazione in Intel 20A con RibbonFET. Dopo la fabbricazione e il test su un chip di prova in silicio, è stato confermato che PowerVia offre un utilizzo altamente efficiente delle risorse del chip, più del 90% delle celle, e un’importante scalabilità dei transistor, consentendo ai progettisti di ottenere maggiori prestazioni ed efficienza nei loro prodotti.

Intel presenterà questi risultati in occasione del VLSI Symposium dall’11 al 16 giugno a Kyoto.

Perché è importante: PowerVia è molto più avanti rispetto alle soluzioni di alimentazione dalla parte posteriore della concorrenza, offrendo ai progettisti di chip, inclusi i clienti di Intel Foundry Services (IFS), un percorso più rapido verso importanti guadagni in termini di consumi e prestazioni nei loro prodotti. Intel ha una consolidata esperienza nell’introduzione di nuove tecnologie nel settore per fare avanzare la legge di Moore, come il silicio teso (strained silicon), il gate metallico Hi-K e FinFET. Con la tecnologia gate-all-around PowerVia e RibbonFET in arrivo nel 2024, Intel continua a guidare il settore nella progettazione di chip e nelle innovazioni di processo.

PowerVia è il primo a risolvere problema dei colli di bottiglia nelle interconnessioni. Un numero sempre crescente di casi d’uso, tra cui l’intelligenza artificiale e la grafica, richiede transistor più piccoli, più densi e più potenti per soddisfare le esigenze di calcolo a essi associate. Da decenni, ormai, le linee di alimentazione e di segnale all’interno dell’architettura di un transistor utilizzano le stesse risorse a scapito uno dell’altra. Separando i due, i chip possono aumentare prestazioni ed efficienza energetica e fornire risultati migliori. L’alimentazione dalla parte posteriore è di vitale importanza per ridurre le dimensioni dei transistor, consentendo ai progettisti di aumentare la densità dei transistor senza sacrificare risorse per fornire più potenza e prestazioni.

Come lo stiamo facendo: Intel 20A e Intel 18A introdurranno sia la tecnologia di alimentazione dalla parte posteriore PowerVia sia la tecnologia Gate-all-around RibbonFET. Trattandosi di un modo completamente nuovo di fornire energia ai transistor, l’implementazione dell’alimentazione dal retro ha sollevato nuove sfide per lo smaltimento del calore i debug.

Disaccoppiando lo sviluppo di PowerVia da RibbonFET, Intel è stata in grado affrontare rapidamente queste sfide per garantire la prontezza per l’implementazione nel silicio basato sui nodi di processo 20A e 18A. gli ingegneri di Intel hanno sviluppato tecniche di mitigazione per evitare problemi di surriscaldamento. La comunità di debug ha inoltre sviluppato tecniche per garantire che la nuova struttura di progettazione potesse essere opportunamente sottoposta a debug. Di conseguenza, l’implementazione del test ha fornito validi parametri di rendimento e affidabilità, dimostrando al contempo il valore intrinseco della tecnologia ben prima che si unisca alla nuova architettura RibbonFET.

Il test ha inoltre fatto uso della progettazione consentite dalla litografia EUV (Extreme Ultraviolet), che ha consentito un utilizzo delle celle standard superiore al 90% su ampie aree del die, con una maggiore densità cellulare che si dovrebbe tradurre in una riduzione dei costi. Il test ha anche mostrato un miglioramento di oltre il 30% nella caduta di tensione della piattaforma e un vantaggio del 6% nella frequenza. Intel ha anche ottenuto caratteristiche termiche nel chip di test PowerVia in linea con le maggiori potenze previste dallo scaling logico.

Prossimi sviluppi: In un terzo documento che sarà presentato al VLSI, il tecnologo di Intel Mauro Kobrinsky spiegherà la ricerca di Intel su modalità più avanzate di implementazione di PowerVia, compresa l’abilitazione del segnale e dell’alimentazione sia sulla parte anteriore sia su quella posteriore del wafer. Portare PowerVia sul mercato in anticipo rispetto agli altri operatori del settore, continuando a innovare, fa parte della lunga tradizione di Intel nel portare costanti avanzamenti al mercato.