Con la tecnologia a 2 nm sarà possibile inserire 50 miliardi di transistor in un chip delle dimensioni di un’unghia

I chip sono la linfa vitale di quasi tutte le tecnologie oggi in uso, dai telefoni cellulari agli elettrodomestici intelligenti e alle automobili, dai server dei data center alle attrezzature per l’esplorazione dello spazio come i rover planetari e i satelliti. La domanda di dispositivi alimentati da chip più veloci ed energeticamente efficienti cresce ogni giorno.

In risposta a tale esigenza, IBM sta per annunciare la nascita del primo chip con tecnologia a 2 nanometri destinato a migliorare le prestazioni del 45% a parità di energia – o a ottenere un risparmio energetico del 75% mantenendo lo stesso livello di prestazioni – rispetto agli attuali chip a 7 nm.

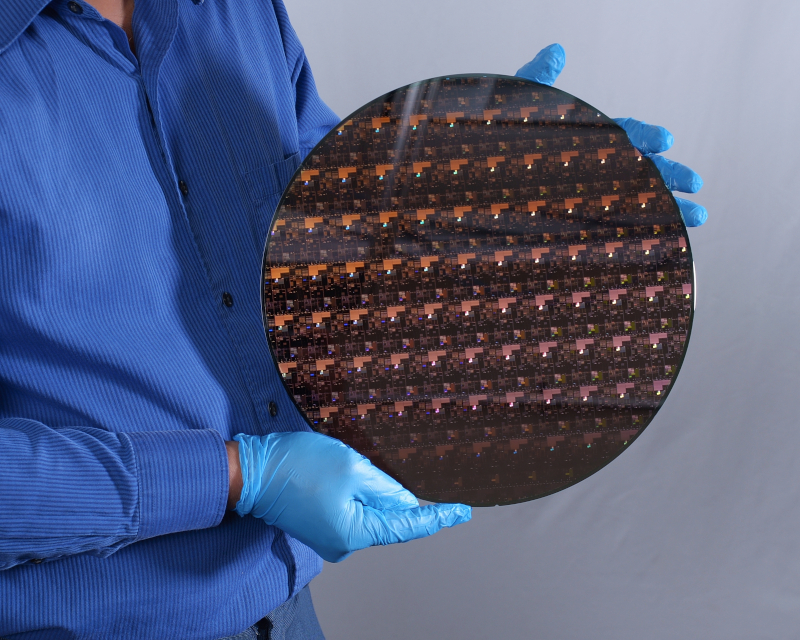

Per mettere le cose in prospettiva, un nanometro vale un miliardesimo di metro. Con la tecnologia a 2 nm sarà possibile inserire 50 miliardi di transistor in un chip delle dimensioni di un’unghia. Ci sono quasi dieci volte più transistor da 2 nm su un wafer da 300 mm che alberi nel mondo.

I potenziali benefici del nuovo chip sono di varia natura. Per esempio, si prevede una riduzione della carbon footprint dei data center, il cui impatto ambientale è oggi in crescita. Se ogni data center cambiasse i propri server con processori basati su 2 nm, si potrebbe risparmiare abbastanza energia da alimentare 43 milioni di abitazioni. Le funzioni di ogni computer portatile incrementeranno la propria velocità, la durata della batteria del cellulare si quadruplicherà, il rilevamento degli oggetti e i tempi di reazione nei veicoli a guida autonoma cambieranno sensibilmente.

La svolta dei 2 nm è stata sviluppata da IBM Research nel laboratorio di Albany, una delle strutture di ricerca sui semiconduttori più avanzate al mondo. È qui che IBM ha costruito un ecosistema di innovazione pubblico-privato che include partner come Samsung Electronics, lo Stato di New York e Intel e che, negli anni, ha portato alla luce scoperte scientifiche e tecnologiche come il primo chip di prova a 7 nanometri nel 2015 e quello a 5 nanometri, con tecnologia nanosheet, due anni più tardi.